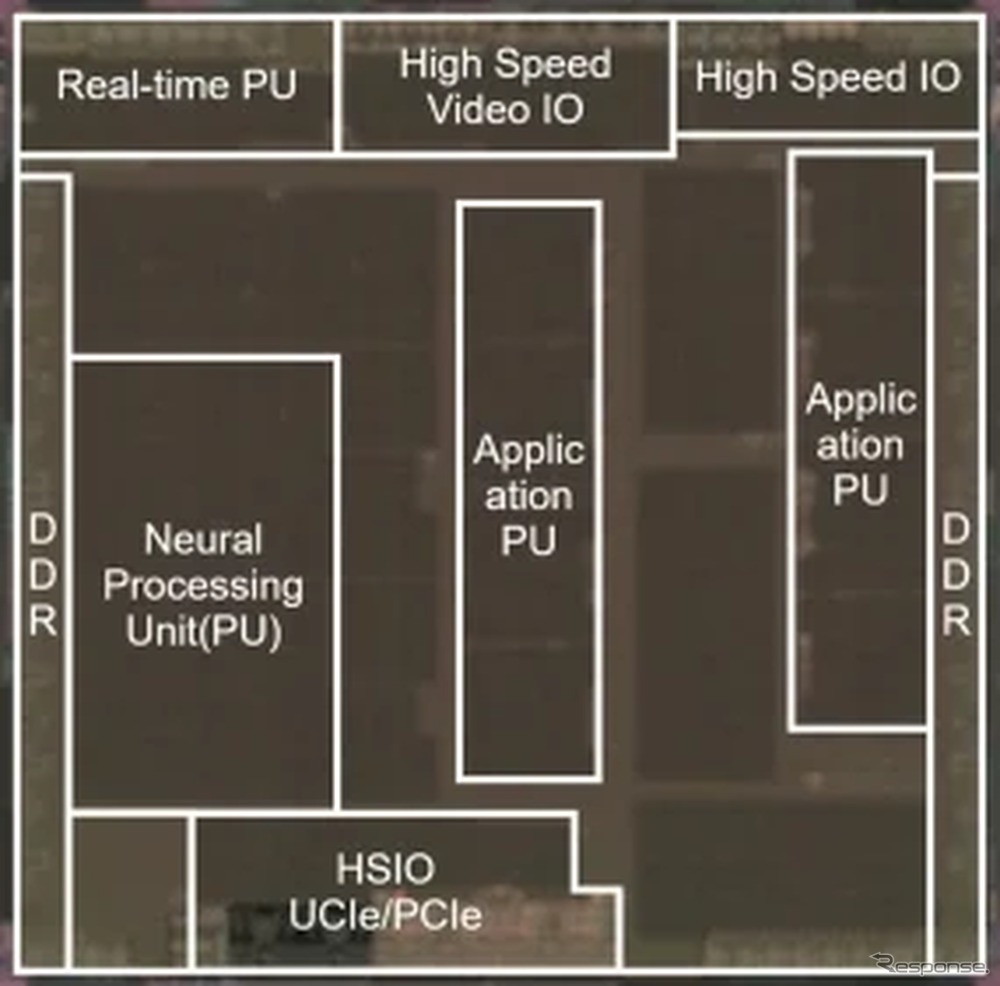

Renesas сообщила о создании сразу трех ключевых технологий, которые должны упростить разработку автомобильных SoC для многодоменных ЭБУ. Речь идет о решениях, рассчитанных на высокую вычислительную нагрузку (в том числе ИИ), поддержку чиплетной компоновки и выполнение жестких требований по функциональной безопасности. Публично эти наработки были представлены 15 февраля 2026 года на конференции ISSCC 2026 в Сан-Франциско.

Почему многодоменные SoC стали «узким местом» в эпоху SDV

Переход к программно-определяемым автомобилям (SDV) меняет требования к электронике: один чип должен параллельно тянуть несколько приложений, масштабироваться за счет микросхем/чиплетов и при этом оставаться безопасным по автомобильным стандартам. Дополнительно усложняет задачу рост самих централизованных SoC: чем выше производительность, тем заметнее энергопотребление, а обеспечение «автомобильного» качества превращается в отдельный вызов.

- нужна высокая производительность для одновременной работы множества функций;

- важна гибкая масштабируемость, в том числе через чиплеты;

- обязательны требования функциональной безопасности для автоприменений;

- при росте мощности возрастает потребление — значит, требуется лучшая энергоэффективность;

- качество и надежность должны сохраняться даже при усложнении архитектуры.

Технология №1: безопасность ASIL D в чиплетной конфигурации

Чтобы закрыть вопрос функциональной безопасности, Renesas разработала архитектуру, способную обеспечивать уровень ASIL D даже тогда, когда SoC собран из чиплетов. В основе — стандарт UCIe для связи die-to-die, дополненный фирменным механизмом RegionID. Такая связка позволяет реализовать защиту от помех (FFI) и не допускать конфликтов при доступе к аппаратным ресурсам, даже если на платформе одновременно выполняется множество приложений.

Как решили проблему RegionID в UCIe

В «обычном» UCIe нет штатной передачи RegionID между кристаллами. Поэтому Renesas предложила метод, при котором RegionID сопоставляется с физическим адресным пространством, затем кодируется и передается через область в UCIe. В результате появляется безопасный контроль доступа к MMU (блоку управления памятью) и ядрам реального времени, а также соблюдаются требования функциональной безопасности на границе чиплетов.

- стандартный UCIe используется как базовый интерфейс die-to-die;

- RegionID добавляет изоляцию и предотвращает взаимные помехи (FFI);

- контроль доступа распространяется на MMU и RT-ядра;

- оценочная пропускная способность «процессор — шина памяти» достигла 51,2 Гбит/с, то есть близка к верхнему пределу внутрисистемных скоростей SoC.

Технология №2: тактирование для крупного NPU на 3-нм процессе и «нулевые дефекты»

Renesas отдельно подчеркнула, что в SDV-эпоху качество «в автомобиле» не менее важно, чем скорость. Поэтому компания переработала подход к тактированию в SoC на 3-нм техпроцессе, где NPU для ИИ-обработки заметно вырос: его площадь стала примерно в 1,5 раза больше, чем у предыдущего поколения. Из-за этого увеличилась задержка распространения тактового сигнала от общего источника до отдельных схем, и синхронизация стала проблемой.

Переход от одного CPG к иерархии с mini-CPG

Ранее генератор тактовых импульсов (CPG) располагался в модульных блоках. Теперь его разделили и внедрили mini-CPG (mCPG) на уровне подмодулей. Такой шаг существенно сократил задержку тактового сигнала и позволил уложиться в требования по таймингу.

Как сохранили тестируемость и надежность

Многослойная структура mCPG усложняет синхронизацию тестовых тактов и мешает достижению «нулевых дефектов», необходимых для автопрома. Чтобы не потерять качество, Renesas встроила тестовую схему в иерархическую архитектуру CPG и обеспечила единый канал связи между пользовательскими и тестовыми часами. В тестовом режиме верхний и нижний mCPG синхронизируются от одного источника, поэтому их можно совместно настраивать как единую фазу. Итог — высокая надежность даже для крупномасштабных SoC, рассчитанных на SDV.

- разделение CPG и размещение mCPG ближе к подмодулям;

- снижение задержек тактового сигнала и выполнение требований по синхронизации;

- интеграция тестовой схемы для единого пути «user/test clock»;

- общий источник в тестовом режиме и настройка единой фазы;

- достижение качества, соответствующего уровню «нулевых дефектов».

Технология №3: тонкая регулировка питания, снижение IR-drop и контроль отказов

Для сочетания производительности, энергоэффективности и безопасности Renesas разработала продвинутую систему управления питанием с более чем 90 областями мощности. Это дает возможность точно подстраивать энергоподачу — от нескольких мВт до нескольких десятков Вт — в зависимости от текущего режима работы.

Два типа силовых выключателей против импульсных токов

С ростом плотности тока при совершенствовании техпроцесса усиливается проблема IR-drop (падения напряжения). Чтобы ее подавить, силовой выключатель (PSW) разделили на два типа:

- кольцевой PSW — на этапе включения питания подавляет импульсный ток;

- рядный PSW — затем выравнивает внутреннее сопротивление.

По оценке компании, это позволило уменьшить IR-drop примерно на 13% по сравнению с традиционным подходом.

ASIL D и DCLS: устойчивость даже при одностороннем сбое

В соответствии с требованиями ASIL D конфигурация Dual Core Lock Step (DCLS) управляет ведущим и контролирующим устройствами через независимые выключатели питания и контроллеры. Благодаря этому обнаружение неисправностей через lock step сохраняется даже при одностороннем отказе. Дополнительно реализован мониторинг: сигнал затвора каждого PSW отслеживается по обратной связи, что помогает фиксировать отключение при возникновении неисправности. Для контроля напряжения применили цифровой монитор DVMON, устойчивый к температурным колебаниям, а стойкость к старению увеличили на 1,4 мВ.

- более 90 доменов питания для точной подстройки потребления;

- снижение IR-drop примерно на 13% за счет двух типов PSW;

- DCLS с независимыми цепями питания для master и checker;

- обратная связь по затворам PSW для диагностики отключений;

- DVMON для стабильного контроля напряжения и повышение устойчивости к старению на 1,4 мВ.

Где это будет применяться: R-Car X5H и многодоменные ЭБУ

Renesas уточнила, что все перечисленные технологии заложены в SoC R-Car X5H, предназначенный для автомобильных многодоменных ЭБУ. По задумке производителя, использование R-Car X5H должно ускорить внедрение SDV и помочь безопасно запускать разнородные приложения — от автономного вождения до цифровой «кабины пилота» — без компромиссов по надежности и функциональной безопасности (источник: response.jp).